试题详情

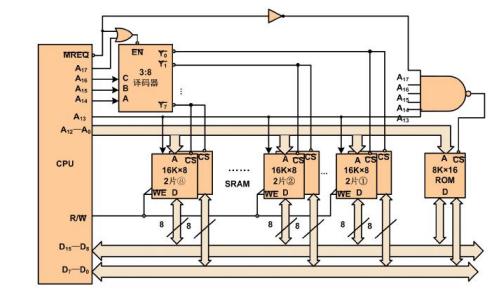

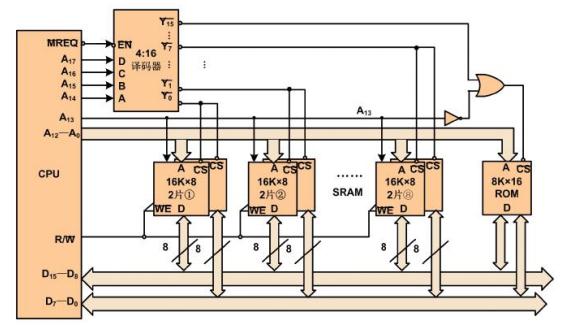

- 简答题某机字长16位,CPU地址总线18位,数据总线16位,存储器按字编址,CPU的控制信号线有:MREQ#(存储器访问请求,低电平有效),R/W#(读写控制,低电平为写信号,高电平为读信号)。试问:【**,★,包捷5.2,编号3.3,3.5.2】 已知该机已有8K×16位的ROM存储器,地址处于主存的最高端;现在再用若干个16K×8位的SRAM芯片形成128K×16位的RAM存储区域,起始地址为00000H,假设SRAM芯片有CS#(片选,低电平有效)和WE#(写使能,低电平有效)信号控制端;试写出RAM、ROM的地址范围,并画出SRAM、ROM与CPU的连接图,请标明SRAM芯片个数、译码器的输入输出线、地址线、数据线、控制线及其连接。

- A.ROM的地址范围

地址为18位,按字(16位)寻址。

R.OM的大小是8K*16bit=213字,则地址数是213个(2000H)。

R.OM处于主存的最高端,地址范围(按十六进制计算):X~3FFFF

3FFFF-X=地址数-1,X=40000-地址数,40000-2000=3E000

所以,地址范围是3E000~3FFFF

B.SRAM的地址范围

S.RAM的大小是128K*16位=217字,则地址数是217个(20000H)

S.RAM处于主存的最低端,地址范围(按十六进制计算):00000~Y

Y.00000=地址数-1,Y=20000-1=1FFFF。

所以,地址范围是00000~1FFFF

C.SRAM的片数

片数=总容量/片大小//单位统一,采用“位”

片数=(128K*16)/(16K*8)=(217*24)/(214*23)=221/217=24=16

d. 使用 3:8 译码器实现

使用 4:16 译码器实现

关注下方微信公众号,在线模考后查看

热门试题

- I/O接口是()与()的中间部分。

- 1.12510的二

- X=-0.1011,Y=0.1010,则

- 单地址指令中,为了完成两个数的算术运算,

- 用1K*4的存储片组成2K*8的内存,则

- 设数据总线上接有A、B、C、D四个寄存器

- DMA数据传送时,DMA控制器会向CPU

- 某机字长16位,CPU地址总线18位,数

- leal指令的目的操作数必须是一个()

- 假设x为8位的定点整数(其中最高位为符号

- 求证:设[x]补=x0,x1,x2&he

- 计算机系统各部件之间传输的信息流是()流

- 只读存储器ROM的特点是通过一定方式将(

- PC的内容是下一条指令存于内存的地址。

- 什么是“程序访问的局部性”?存储系统中哪

- 执行:500LOAD$20,R1,则操作

- 变址器中为1000,形式地址为50,则有

- 一条转移指令的操作过程包括取指令、指令译

- 计算机执行指令分为取指令、分析指令、执行

- 某计算机字长是64位它的存储容量是1MB