试题详情

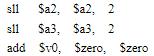

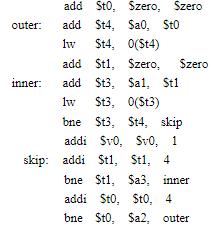

- 简答题 下列指令序列用来对两个数组进行处理,并产生结果存放在$v0中。假定每个数组有2500个字,其数组下标为0到2499。两个数组的基地址分别存放在$a0和$a1中,数组长度分别存放在$a2和$a3中。要求为以下MIPS指令序列加注释,并简单说明该过程的功能。假定该指令序列运行在一个时钟频率为2GHz的处理器上,add、addi和sll指令的CPI为1;lw和bne指令的CPI为2,则最坏情况下运行所需时间是多少秒?

-

关注下方微信公众号,在线模考后查看

热门试题

- 已知x=10,y=–6

- 说明beq指令的含义,并解释为什么汇编程

- Amdahl定律中“可改进比例”指可改进

- 根据指令系统结构划分,现代计算机包含哪两

- MIPS是测量计算机性能的一致性指标。

- 写调块策略是用于写操作失效时的策略。

- 寻址技术

- 在MIPS指令集中需要增加一条swap指

- 综合考虑不同的存储器实现技术,我们会发现

- 按照产生失效的原因不同,Cache失效可

- DLX的浮点操作有加、减、乘、除。后缀D

- Tandem公司发表的Cyclone高可

- 多操作数指令可以是单字长指令

- 简述减小Cache失效开销的几种方法。

- 在IEEE754标准中,浮点数的表示采用

- 根据Amdahl定律,系统加速比由哪两个

- 可以说向后兼容是系列机的根本特征。

- 非阻塞Cache

- 根据CPU内部存储单元类型对指令集结构进

- 按照同一时间内各段之间的连接方式来分,流