试题详情

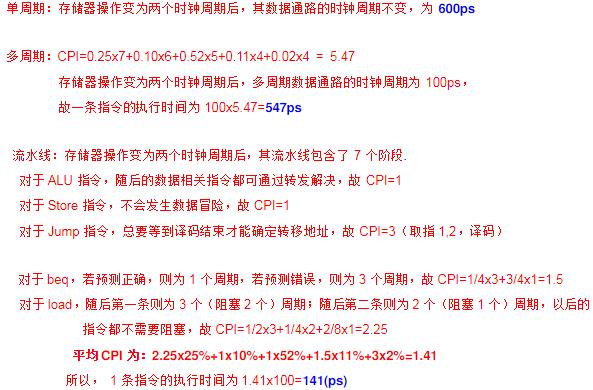

- 简答题 假设数据通路中各主要功能单元的操作时间为:存储单元:200ps;ALU和加法器:100ps;寄存器堆读口或写口:50ps。程序中指令的组成比例为:取数25%、存数10%、ALU52%、分支11%、跳转2%。假设时钟周期取存储器存取时间的一半,MUX、控制单元、PC、扩展器和传输线路等的延迟都忽略不计,则下面的实现方式中,哪个更快?快多少? (1)单周期方式:每条指令在一个固定长度的时钟周期内完成; (2)多周期方式:每类指令时钟数:取数-7,存数-6,ALU-5,分支-4,跳转-4; (3)流水线方式:取指1、取指2、取数/译码、执行、存取1、存取2、写回7段流水线;没有结构冒险;数据冒险采用“转发”技术处理;load指令与后续各指令之间存在依赖关系的概率分别1/2、1/4、1/8、…;分支延迟损失时间片为2,预测准确率为75%;不考虑异常、中断和访问失效引起的流水线冒险。

-

关注下方微信公众号,在线模考后查看

热门试题

- 根据指令系统功能结构的不同,计算机体系结

- 寻址方式按操作数的物理位置不同,多使用(

- 流水CPU中的主要问题是()相关、()相

- 假定某计算机字长16位,没有cache,

- VictimCache

- 在计算机中,衡量互连网络性能好坏的主要因

- 数据通路出错引起的中断是()

- 若一次加法需要1ns,一次移位需要0.5

- 什么是向量链接技术?

- 微程序设计技术是利用软件方法设计操作控制

- 在DLX指令实现的简单数据通路中,IF是

- 假定某计算机工程师想设计一个新CPU,一

- 总线的主要缺点是()。

- 假设一个同步总线的时钟频率为50MHz,

- 假定某计算机字长16位,没有cache,

- 解决虚拟Cache的清空问题的方法是什么

- 在向量处理机中,链接只能在顺序的Conv

- 在指令集结构的功能设计中,所有的指令集一

- 数据对存储位置的限制比指令的少,因此更便

- “虚拟索引+物理标识”Cache的基本思