试题详情

- 简答题

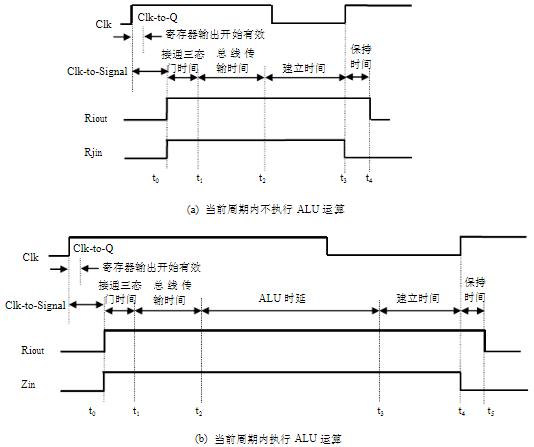

如图,假定总线传输延迟和ALU运算时间分别是20ps和200ps,寄存器建立时间为10ps,寄存器保持时间为5ps,寄存器的锁存延迟(Clk-to-Q time)为4ps,控制信号的生成延迟(Clk-to-signal time)为7ps,三态门接通时间为3ps,则从当前时钟到达开始算起,完成以下操作的最短时间是多少?各需要几个时钟周期?

将数据从一个寄存器传送到另一个寄存

将数据从一个寄存器传送到另一个寄存

-

器寄存器的锁存延迟与控制信号的生成延迟的时间重叠,且Clk-to-signal time> Clk-to-Q time,所以完成寄存器传送的时间延迟为:7+3+20+10=40ps。

因为在这个过程中,只要最后保存一次信息到寄存器,所以只需要一个时钟周期。 关注下方微信公众号,在线模考后查看

热门试题

- 广义来说,并行性即包含()性,又包含()

- 在消息传递通信机制的硬件上怎样支持共享存

- 指令系统中指令的编码方法不包括以下哪一种

- 在Cache中,只要增加块容量,一定可以

- 简述直接相联映象规则。

- 区别模拟和仿真

- 磁盘的数据传输率有两个,一是()的内部传

- 解决虚拟Cache的清空问题的方法是什么

- 流水线中有哪三种相关?各是什么原因造成的

- I/O性能评价的指标主要包括:设备类型、

- 目前公认的相对可靠的性能评价方法,是使用

- 解释重叠方式中的“一次重叠”的含义。

- 实现集中式共享存储器体系结构一致性的基本

- 计算机系统“由中间开始设计”,其“中间”

- 层次机构

- 程序的局部性包含程序的()局部性和程序的

- 系列机软件兼容必须做到向()兼容,尽可能

- 何谓分布式共享存储器结构机器?此种结构有

- 实现Cache一致性协议时,有哪两种跟踪

- MIPS和MFLOPS是计算机性能衡量的