试题详情

- 简答题设计一个代码转换电路,将1位十进制数的余3码转换成2421码

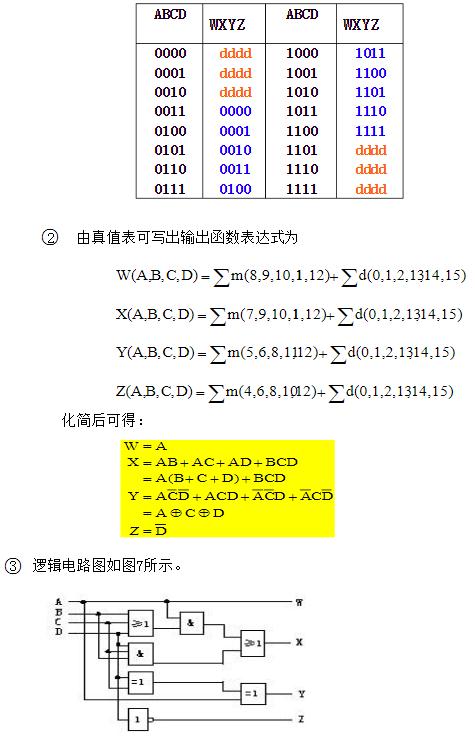

- ①设1位十进制数的余3码为ABCD,相应2421码为WXYZ,根据余3码和2421码的编码法则,可作出真值表如表所示。

关注下方微信公众号,在线模考后查看

热门试题

- 若要设计一个脉冲序列为110100111

- 逻辑函数=()

- 对于T触发器,若原态Qn=1,欲使新态Q

- 添加项公式的对偶式为()

- 简述大规模数字逻辑电路设计中的自上而下设

- 一个同步正常工作时,不允许输入R+S=1

- Mealy型时序电路的输出只与当前的外部

- 写出多选则控制条件语句的编程格式,并简述

- 分析下图所示的逻辑电路,写出表达式并进行

- 设计一个模65的同步计数器,至少需要()

- 具有“置0”“置1“保持”和“计数翻转”

- 将模拟信号转换为数字信号,需要经过()、

- 一个四输入与非门,使其输出为0的输入变量

- 集成电路的4个电流参数分别是:()、()

- 分析下图给定的组合逻辑电路,写出输出P<

- 一位十进制计数器至少需要()个触发器。

- 十进制数(0.7875)10<

- 以下电路中,加以适当辅助门电路,()适于

- 待编码信号数为个,输出代码位数为n位,它

- 按功能的不同,译码器可分为:()、()