试题详情

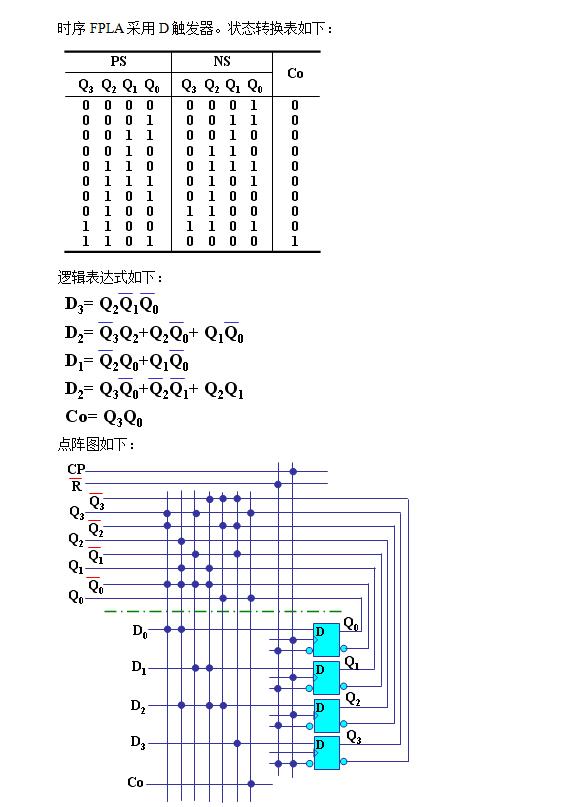

- 简答题用时序FPLA设计一个循环码十进制计数器。要求设计优化,即FPLA的面积尽可能小。

关注下方微信公众号,在线模考后查看

热门试题

- 数字电路按照是否有记忆功能通常可分为两类

- 采用5V电源的CMOS器件的高电平范围为

- 一个16选一的数据选择器,其地址输入(选

- 下列各门电路中,()的输出端可直接相连,

- n级触发器构成的环形计数器,其有效循环的

- 分析图所示的组合逻辑电路,说明电路功能,

- 与普通代数相比逻辑代数有何特点?

- 分析图中时序逻辑电路,要求: (1)指出

- 八路数据选择器应有()个选择控制器。

- 用1024×1的RAM接成1024×8的

- 已知某一时序电路的状态方程为 求:当X

- 简述编译器在进行项目编译时的所进行的工作

- 简述硬件描述语言的涵义及特点。

- 停电重新上电后,EEPROM存储器内容会

- 试将2048×2位的RAM扩展为2048

- (48)10=()

- ()的输出端可直接相连,实现线与逻辑功能

- 对于共阳接法的发光二极管数码显示器,应采

- 分析如图所示逻辑电路,说明该电路功能。

- 给36个字符编码,至少需要()位二进制数