试题详情

- 简答题

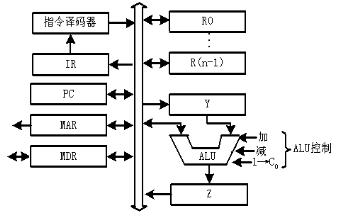

假定某计算机字长16位,CPU内部结构如图所示,CPU和存储器之间采用同步方式通信,按字编址。采用定长指令字格式,指令由两个字组成,第一个字指明操作码和寻址方式,第二个字包含立即数Imm16。若一次存储访问所花时间为2个CPU时钟周期,每次存储访问存取一个字,取指令阶段第二次访存将Imm16取到MDR中,请写出下列指令在指令执行阶段的控制信号序列,并说明需要几个时钟周期。

将立即数Imm16加到寄存器R1中,此时,Imm16为立即操作数。即:R[R1]←R[R1]+ Imm16

将立即数Imm16加到寄存器R1中,此时,Imm16为立即操作数。即:R[R1]←R[R1]+ Imm16

-

关注下方微信公众号,在线模考后查看

热门试题

- 透明性

- 浮点数尾数下溢的处理方法

- 若主存块地址i=(10101)B,CAC

- MIMD成为通用多处理机体系结构选择的因

- 假设流水线各段的时间相等,均为△t,则最

- 根据CPU性能公式,程序的执行时间等于(

- CRAY-1向量机相邻向量指令之间,既无

- 假定某计算机的CPU主频为500MHz,

- 何为流水线效率?为何流水线效率不能达到1

- 实现Cache一致性协议有哪两类?

- 引起Cache与主存内容不一致的原因是什

- 多端口存储器适合于连接()。

- Amdahl定律中“部件加速比”指可改进

- 简述存储程序计算机(冯·诺依曼结构)的特

- 在存储器层次结构设计中,论述首先要解决的

- 计算机系统“由中间开始”设计,其“中间”

- 试以系列机为例,说明计算机系统结构、计算

- 采用多处理机的一致性机制实现旋转锁有什么

- 简述机群系统的特点?

- 单级存储器的主要矛盾是什么?通常采取什么