试题详情

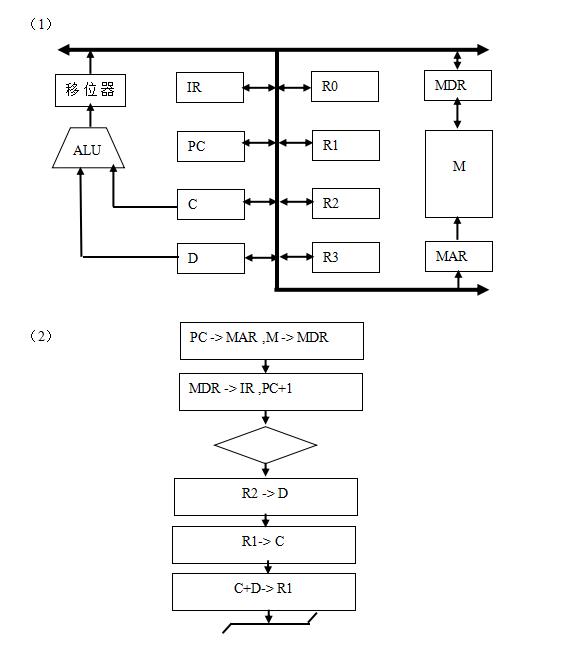

- 简答题某计算机有如图所示的功能部件,其中M为主存,MDR为主存数据寄存器,MAR为主存地址寄存器,R0~R3为通用寄存器,IR为指令寄存器,PC为程序计数器(具有自动加1功能),C,D为暂存器,ALU为算术逻辑单元,移位器可以左移、右移、直通传送。 (1)将功能部件连接起来,组成完整的数据通路,并用单向或者双向箭头表示信息传送方向。 (2)画出“ADDR1,R2”指令周期流程图。该指令的含义是将R1中的数与R2中的数相加,相加的结果直通传送至R1中。

关注下方微信公众号,在线模考后查看

热门试题

- 在不改变中断响应优先级次序的条件下,通过

- 地址总线A0(高位)~A15(低位),若

- 对存储器的要求是(),成本低。为了解决这

- 组合逻辑控制是一种硬布线控制,组合逻辑线

- 开中断使用()指令。

- 下面所列的(),不属于系统总线接口的功能

- 以下关于DRAM和SRAM说法错误的是(

- 下面哪一项不是冯·诺依曼型计算机的最根本

- 某存储器容量为32K×16位,则()。

- IR的内容是读内存的地址。

- 浮点表示:数字5用浮点表示时的小数字段f

- 运算中会产生溢出的是()

- 字符型编码是用()的形状来进行的编码。

- 下列关于量化评价一个程序中局部性简单原则

- 若采用双符号位,则两个负数相加产生溢出时

- 主控部件与被控部件采用同一定时系统称为(

- 为方便判断结果溢出,补码加减运算采用()

- 启动一次存储器操作到完成该操作所经历的时

- 将指令Cache和数据Cache分开又有

- 考虑下面的函数,假设调用copy_arr