试题详情

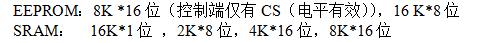

- 简答题CPU的地址总线16根(A15-A0,A0是低位),双向数据总线16根(D15-D0),控制总线中与主存有关的信号有/MREQ(允许访存,低电平有效),R/W(高电平读命令,低电平写命令)。主存地址空间分配如下:0~8191为系统程序区,由EPROM芯片组成,从8192起一共32k地址空间为用户程序区,最后(最大地址)4k地址空间为系统程序工作区。上述地址为10进制,按字编址。现有如下芯片:

请从上述芯片中选择芯片设计该计算机主存储器,画出主存逻辑框图,注意画选片逻辑(可选用门电路及译码器)。

请从上述芯片中选择芯片设计该计算机主存储器,画出主存逻辑框图,注意画选片逻辑(可选用门电路及译码器)。

关注下方微信公众号,在线模考后查看

热门试题

- 在什么条件下,I/O设备可以向CPU提出

- 贯穿整个系统的一组电子管道称作()

- CPU的基本组成部分包括运算器、Cach

- 下列选项不是输入设备的是()。

- 假设一个4位数值(用十六进制数字0~F表

- 比较硬连线控制器和微程序控制器,下列说法

- 数字计算机有哪些主要应用?

- 指令译码

- RAM中每个存储单元为16位,则下面所述

- 零的原码可以用以下哪个代码表示()

- 假设一个基于IEEE浮点格式的5位浮点表

- 用1K*4的存储片组成2K*8的内存,则

- MROM中的内容由()。

- 有两个浮点数 x=2(+01)

- 关于消除循环的低效率,下列说法不正确的是

- 根据题目的描述,写出最匹配的词或短语;在

- 在控制器的控制信号中,相容的信号是()信

- 以下哪些措施可能提高程序并行性()

- 建立高速缓冲存储器的理论依据是()。

- 以下关于DRAM和SRAM说法错误的是(