试题详情

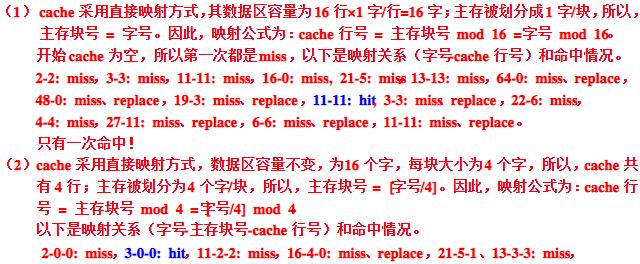

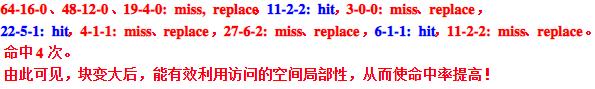

- 简答题 假定某计算机的cache共16行,开始为空,块大小为1个字,采用直接映射方式。CPU执行某程序时,依次访问以下地址序列:2,3,11,16,21,13,64,48,19,11,3,22,4,27,6和11。要求: (1)说明每次访问是命中还是缺失,试计算访问上述地址序列的命中率。 (2)若cache数据区容量不变,而块大小改为4个字,则上述地址序列的命中情况又如何?

-

关注下方微信公众号,在线模考后查看

热门试题

- 目前有一种日渐普及的测试程序产生方法,就

- 解决重叠和流水中的操作数相关,主要包括推

- “线延迟墙”指的是什么?技术的发展趋势;

- 评价存储系统性能时,CPU时间=IC×[

- 模拟与仿真的主要区别和适合场合是什么?

- 消除流水线的瓶颈段有哪些方法?

- RAID3

- 划分多级层次结构的作用是什么?

- 虚拟存储器常用的地址映象方式是()。

- 磁盘访问时间与以下4个时间有关()、()

- 指令集结构

- 闪速存储器能提供高性能.、低功耗、高可靠

- 按照Cache产生失效的原因不同,可以把

- 减少流水线处理分支指令时的暂停时钟周期数

- 数据相关

- 指令集格式设计时,有哪三种设计方法?

- 现代计算机中,流水线按处理级别可分为三级

- 当流水线中数据和指令存在同一存储器中时,

- DLX流水线可以分为()、()、()、(

- 计算机系统的设计者需要掌握技术的发展,尤