试题详情

- 简答题

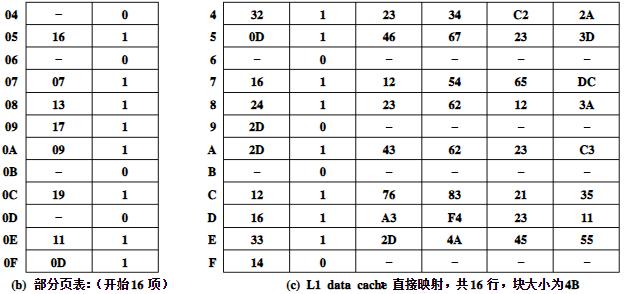

假定一个计算机系统中有一个TLB和一个L1 data cache。该系统按字节编址,虚拟地址16位,物理地址12位;页大小为128B,TLB为四路组相联,共有16个页表项;L1 data cache采用直接映射方式,块大小为4B,共16行。在系统运行到某一时刻时,TLB、页表和L1 data cache中的部分内容(用十六进制表示)如下:

CPU从地址067AH中取出的值为多少?说明CPU读取地址067AH中内容的过程。

CPU从地址067AH中取出的值为多少?说明CPU读取地址067AH中内容的过程。

- 地址067AH=0000 0110 0111 1010B,所以,虚页号为0000011 00B,映射到TLB的第00组,将0000011B=03H与TLB第0组的四个标记比较,虽然和其中一个相等,但对应的有效位为0,其余都不等,所以TLB缺失,需要访问主存中的慢表。直接查看0000011 00B =00CH处的页表项,有效位为1,取出物理页号19H=11001B,和页内偏移111 1010B拼接成物理地址:11001 111 1010B。根据中间4位1110直接找到cache第14行(即:第E行),有效位为1,且标记为33H=110011B,正好等于物理地址高6位,故命中。根据物理地址最低两位10,取出字节2中的内容4AH=01001010B。

关注下方微信公众号,在线模考后查看

热门试题

- 计算机系统结构来看,机器语言程序员看到的

- 磁盘访问时间与以下4个时间有关:寻道时间

- 下列()不属于应用软件的范畴

- Omega网络采用()。

- 响应时间必须通过运行“真实程序”获得。

- 广义来说,并行性即包含()性,又包含()

- Cydrome公司的Cydra5计算机属

- 组相联映射

- 指令系统的完整性

- Amdahl定律表明系统的加速比依赖于(

- 闪速存储器称为()。

- 在向量处理的链接技术中,向量链接要保证无

- 减少流水线处理分支指令时的暂停时钟周期数

- 简述计算机采用多级层次结构的必要性和可能

- 平均每条指令的执行周期数(CPI)与程序

- 已知x=10,y=–6,采用6位机器数表

- 不同的CRT显示标准所支持的最大()和(

- 解释子块放置技术。

- MO型光盘和PC型光盘都是()型光盘。

- “一次重叠”解释时,第K+1条指令需等第