试题详情

- 简答题某机字长16位,CPU地址总线18位,数据总线16位,存储器按字编址,CPU的控制信号线有:MREQ#(存储器访问请求,低电平有效),R/W#(读写控制,低电平为写信号,高电平为读信号)。试问:【**,★,包捷5.2,编号3.3,3.5.2】 已知该机已有8K×16位的ROM存储器,地址处于主存的最高端;现在再用若干个16K×8位的SRAM芯片形成128K×16位的RAM存储区域,起始地址为00000H,假设SRAM芯片有CS#(片选,低电平有效)和WE#(写使能,低电平有效)信号控制端;试写出RAM、ROM的地址范围,并画出SRAM、ROM与CPU的连接图,请标明SRAM芯片个数、译码器的输入输出线、地址线、数据线、控制线及其连接。

- A.ROM的地址范围

地址为18位,按字(16位)寻址。

R.OM的大小是8K*16bit=213字,则地址数是213个(2000H)。

R.OM处于主存的最高端,地址范围(按十六进制计算):X~3FFFF

3FFFF-X=地址数-1,X=40000-地址数,40000-2000=3E000

所以,地址范围是3E000~3FFFF

B.SRAM的地址范围

S.RAM的大小是128K*16位=217字,则地址数是217个(20000H)

S.RAM处于主存的最低端,地址范围(按十六进制计算):00000~Y

Y.00000=地址数-1,Y=20000-1=1FFFF。

所以,地址范围是00000~1FFFF

C.SRAM的片数

片数=总容量/片大小//单位统一,采用“位”

片数=(128K*16)/(16K*8)=(217*24)/(214*23)=221/217=24=16

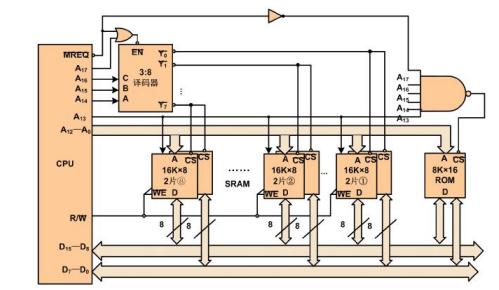

d. 使用 3:8 译码器实现

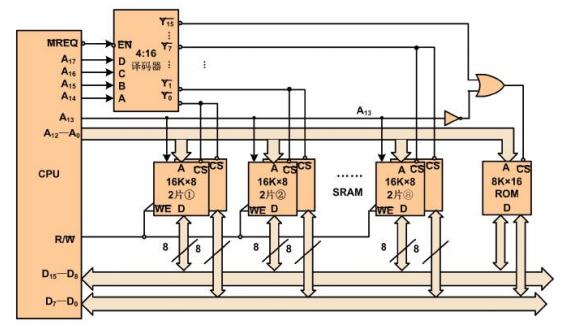

使用 4:16 译码器实现

关注下方微信公众号,在线模考后查看

热门试题

- 已知:X=0.1011,Y=—0.110

- 控制单元的功能是什么?其输入受什么控制?

- 计算机系统由哪些部分组成?硬件由哪些构成

- 指令的顺序寻址是从下列哪个寄存器在获得指

- 在一地址指令格式中,可能有(),也可能有

- CPU响应中断时,最先完成的两个步骤是(

- RAM芯片串联时可以()

- 下例数据代码设为奇校验,请在括号中填入相

- 静态MOS存储器与动态MOS存储器存储信

- 现有如下存储芯片:2K×1的ROM、4K

- 与微程序控制器相比,硬件布线控制器的特点

- 下列说法中正确的是()。

- 改善计算机性能的重要技术途径是()

- 已知下列数字的ASCII码,8421码和

- n+1位定点整数的补码表示范围是()。

- 下列不属于浮点运算器的部件是()

- DMA控制器与CPU分时使用主存的控制方

- 假设你的职业是卡车司机,你运送一车土豆从

- 什么情况下需要总线仲裁?总线仲裁的目的是

- 内存地址译码器分为()译码器。