试题详情

- 简答题设计一个正弦波发生器,通过计数器连续读取ROM中预存的波形码数据,送给DAC,转换为模拟电压后再经低通滤波器做平滑滤波,合成线性度较好的正弦波。

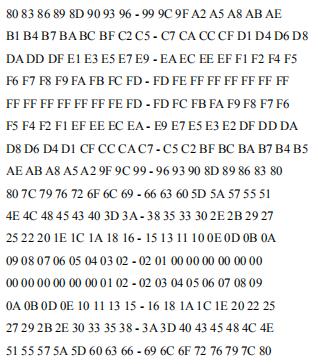

- 一个周期内正弦波码表样点越多,波形越好,这里采用256点正弦波存入ROM。使用8位二进制计数器作为地址发生器顺序访问,将读出的ROM数据直接送给DAC即可。

256点正弦波码表样值数据如下:

正弦波(0700~07FFH)

关注下方微信公众号,在线模考后查看

热门试题

- 时序逻辑电路在结构上存在输出到输入的()

- 简述粗粒度FPGA和细粒度FPGA各自的

- 分析下图电路功能。

- n个变量构成的最小项mi

- 写出T触发器的特征方程()

- 如下图(a)、(b)、(c)和(d)所示

- 双稳态触发器的基本特征是什么?

- 全面描述一时序逻辑电路的功能,必须使用三

- CPLD是指()可编程逻辑器件。

- 十六进制数3A.B对应的八进制数是()

- 已知下列逻辑函数,试用卡诺图分别求出Y1

- 如下图所示,主从JK触发器电路中,CP和

- RAM由若干位存储单元组成,每个存储单元

- 十六进制数F6.A转换成八进制数为()

- 电平异步时序逻辑电路不允许两个或两个以上

- (10110010.1011)

- 八路数据选择器应有()个选择控制器。

- 试分析图所示电路的逻辑功能。列出状态转换

- 已知双4选1数据选择器74LS153的逻

- 下面与八进制数(47.3)8<