试题详情

- 简答题简述ARMJTAG调试接口结构、电路与功能。

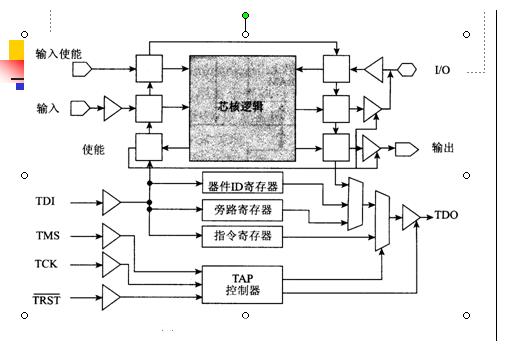

- ARMJTAG调试接口的结构如图所示。它由测试访问端口TAP(Test Access Port)控制器、旁路(Bypass)寄存器、指令寄存器、数据寄存器以及与JTAG接口兼容的ARM架构处理器组成。处理器的每个引脚都有一个移位寄存单元(边界扫描单元(BSC,Boundary Scan Cell)),它将JTAG电路与处理器核逻辑电路联系起来,同时,隔离了处理器核逻辑电路与芯片引脚。所有边界扫描单元构成了边界扫描寄存器BSR,该寄存器电路仅在进行JTAG测试时有效,在处理器核正常工作时无效。

(1)JTAG的控制寄存器

①测试访问端口TAP控制器对嵌入在ARM处理器核内部的测试功能电路进行访问控制,是一个同步状态机。通过测试模式选择TMS和时钟信号TCK来控制其状态转移,实现IEEE1149.1标准所确定的测试逻辑电路的工作时序。

②指令寄存器是串行移位寄存器,通过它可以串行输入执行各种操作的指令。

③数据寄存器组是一组串行移位寄存器。操作指令被串行装入由当前指令所选择的数据寄存器,随着操作的进行,测试结果被串行移出。

关注下方微信公众号,在线模考后查看

热门试题

- 创建的shell变量,默认为()

- 嵌入式系统的BooTLoader的功能是

- 引导装入程序在系统加电之后会加载操作系统

- 下列不是嵌入式系统特点的是()

- S3C2410A与触摸屏接口有几种接口模

- 简述ARMJTAG调试接口结构、电路与功

- 分析下列每条语句,并说明程序实现的功能。

- 简述Windows CE的特点

- 若基于Linux操作系统所开发的ARM应

- 状态寄存器的SF标志位是进位标志。

- 嵌入式系统使用的存储器有多种类型,按照其

- DSP处理器由于本身的设计适合执行DSP

- 请分别写出调用子程序、子程序返回所使用的

- 液晶工作在文本模式下时,既可以显示英文字

- 当异常发生时,寄存器()用于保存CPSR

- μC/OS-II操作系统的内核非常小,其

- 什么是大端模式?什么是小端模式?请举例说

- 分析在四线连接方式的RS485组网方式中

- 某系统需要永久存放大量不再修改的数据,最

- 谈一谈嵌入式处理器的发展趋势。