试题详情

- 简答题设计一块数字秒表,能够精确反映计时时间,并完成复位、计时功能。秒表计时的最大范围为1小时,精度为0.01秒。秒表可得到计时时间的分、秒、0.1秒等度量,且各度量单位可以正确进位;当复位清零有效时,秒表清零并做好计时准备。在任何情况下,只要按下复位开关,秒表都要无条件地进行复位操作,即使在计时过程中也要无条件地清零;设置秒表启动/停止开关。按下该开关,秒表即刻开始计时,并得到计时结果;放开该开关时,计时停止。

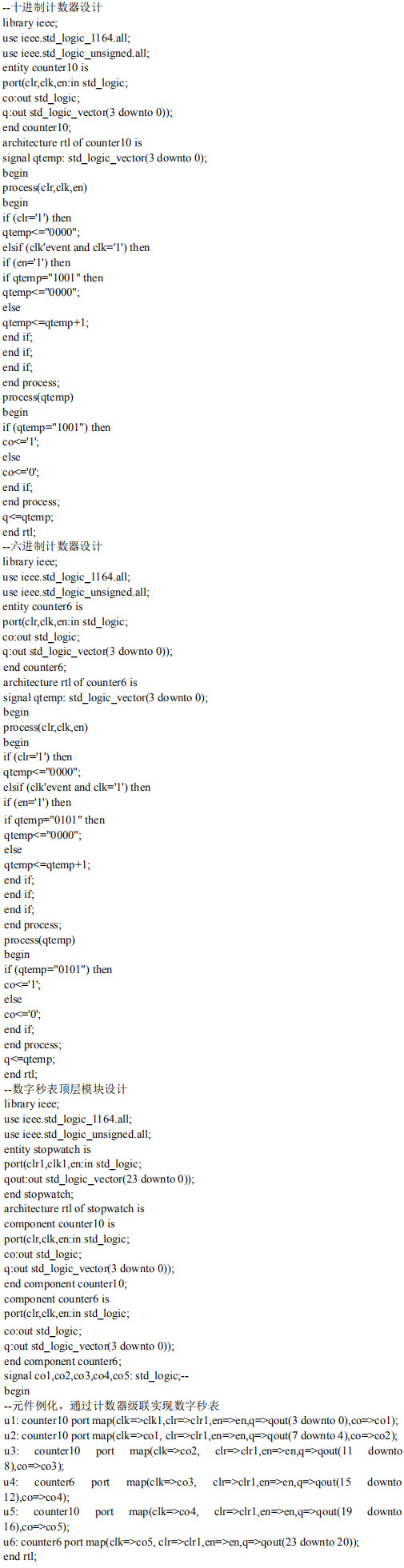

- 设计分析:根据上述设计要求,可以预先设计若干个不同进制的计数器单元模块,然后将其进行例化组合来得到数字秒表系统。要满足数字秒表的精度,首先要获得精确的计时基准信号,这里的系统精度要求为0.01秒,因此必须设置周期为0.01秒的时钟脉冲。0.01秒、0.1秒、秒、分等计时单位之间的进位转换可以通过不同进制的计数器实现。设置十进制计数器和六进制计数器,每位计数器均能输出相应计时单位计数结果,其中,十进制计数器可以实现0.01秒、0.1秒、秒、分为单位的计数,六进制计数器可以实现以10秒、10分为单位的计数。把各级计数器级联,即可同时显示0.01秒、0.1秒、1秒、1分钟。级联可分为串行进位方式和并行进位方式。在串行进位方式中,以低位片的进位输出信号作为高位片的时钟输入信号。在并行进位方式中,以低位片的进位输出信号作为高位片的工作状态信号(计数的使能信号en),两片的clk端同时接计数输入信号。

VHDL源代码如下:

关注下方微信公众号,在线模考后查看

热门试题

- 某热水器如下图所示:图中虚线表示水位,A

- CMOS数字集成电路与TTL数字集成电路

- 存储容量是()

- 已知某一时序电路的状态方程为 求:当X

- ROM由地址译码器,(),()三部分功能

- 组合电路不含有记忆功能的器件。

- CMOS逻辑门电路可以直连TTL负载。

- TTL与非门电压传输特性曲线分为()区、

- CMOS或非门与TTL或非门的逻辑功能完

- 用异或门设计一个三变量奇校验电路,当输入

- 设8位T型电阻网络DAC如图所示,已知U

- 最简电路是否一定最佳?为什么?

- 在CP作用下,欲使D触发器具有的功能,其

- 同步时序电路由组合电路和存储器两部分组成

- 一般来说,时序逻辑电路中所需的触发器n与

- 电路如图(a)所示,假设初始状态Q

- 最小项,顾名思义就是指的乘积项中变量个数

- 分析下图所示的逻辑电路,写出表达式并进行

- 以下四种转换器,()是A/D转换器且转换

- 若两个函数具有相同的真值表,则两个逻辑函