试题详情

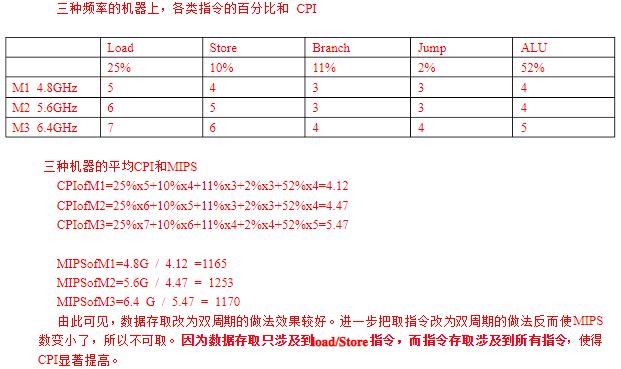

- 简答题对于多周期MIPS处理器,假定将访问数据的过程分成两个时钟周期可使时钟频率从4.8GHz提高到5.6GHz,但会使得lw和sw指令增加时钟周期数。已知基准程序CPUint 2000中各类指令的频率为:Load:25%,Store:10%,Branch:11%,Jump:2%,ALU:52%。以基准程序CPUint 2000为标准计算时钟频率提高后处理器的性能提高了多少?若将取指令过程再分成两个时钟周期,则可进一步使时钟频率提高到6.4GHz,此时,时钟频率的提高是否也能带来处理器性能的提高?为什么?

-

关注下方微信公众号,在线模考后查看

热门试题

- 经多级网络串联来实现全排列网络,只能用(

- 可以说向后兼容是系列机的根本特征。

- 写合并

- 指令之间的名相关有()和()两种。

- 某双面磁盘,每面有220道,已知磁盘转速

- 在Cache中,只要增加块容量,一定可以

- 实现下列各数的转换。(25.8125)<

- ()型操作系统适合于工作负荷固定、处理机

- 在衡量计算机系统可靠性的性能指标中,()

- 集中式仲裁有几种方式?

- 流水线的效率在满负荷运行时可达1。

- ()表示法主要用于表示浮点数中的阶码。

- 采用组相联映像的Cache存储器,为提高

- 冲突失效是指在()映象或()映象Cach

- 在计算机系统设计中,比较好的方法是()。

- 0~15共16个处理单元用单级PM2-3

- 在IEEE754标准中,浮点数的表示采用

- 计算机的设计受两方面的影响:一方面是()

- 故障、错误和失效三者之间的关系是什么?

- 和具有m个并行部件的处理器相比,一个m段