试题详情

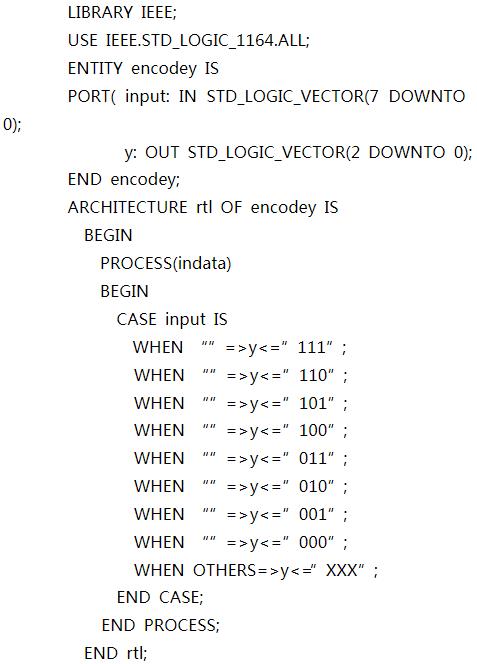

- 简答题下述程序是一个8-3编码器的VHDL语言程序,说明该程序的工作流程。

- 该程序首先调用IEEE库,并在实体中定义了全局输入信号矢量input(8)和输出信号矢量y(3),构造体中的进程语句描述由8位输入信号译码得到3位输出信号的关系。

关注下方微信公众号,在线模考后查看

热门试题

- 某存储器具有8根地址线和8根双向数据线,

- 一个基本RS触发器在正常工作时,它的约束

- 用逻辑代数的基本公式和定律将下列逻辑函数

- 设计一个串行数据检测电路,当连续输入3个

- 简述PLD的涵义。

- 比较TTL和CMOS逻辑电路各有什么优缺

- (10110010.1011)

- 伴随着()器件出现,逻辑函数的表示方法开

- 如果已知X+Y和X·Y的逻辑值相同,那么

- 简述时序仿真的作用及目的。

- 完成两个1位二进制数相加的电路称为()

- 试用真值表验证下列表达式:

- 写出多选则控制条件语句的编程格式,并简述

- 分析下图所示的同步时序电路 1)写出触发

- 主从JK触发器、边沿JK触发器和同步JK

- FPGA是指()可编程门阵列。

- 下列等式不成立的是()

- 某移位寄存器的时钟脉冲频率为100KHZ

- 用八选一数据选择器实现下列函数:

- 某函数的卡诺图如图所示 (1)若b=a