试题详情

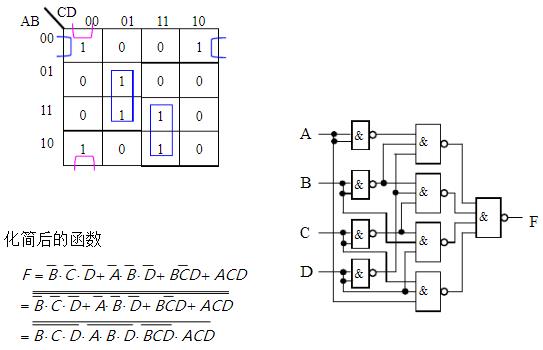

- 简答题试用与非门设计实现函数F(A,B,C,D)=Σm(0,2,5,8,11,13,15)的组合逻辑电路。

- 首先用卡诺图对函数进行化简,然后变换成与非-与非表达式。

关注下方微信公众号,在线模考后查看

热门试题

- 锁存器是对()敏感的器件,而触发器为对(

- 构成移位寄存器不能采用的触发器为()

- 画D触发器的输出端Q1

- 电平异步时序逻辑电路不允许两个或两个以上

- 占空比的公式为:q=tw

- 已知某电路的真值表如下,该电路的逻辑表达

- “0”的补码只有一种形式。

- 简述8位模型计算机基本结构与原理。

- D触发器的特征方程Qn+1

- 时序逻辑电路的功能表示方法有()、()、

- 构造一个十进制的异步加法计数器,需要多少

- 构成一个5进制计数器需要5个触发器。

- 试用PROM实现8421BCD转换为格雷

- 异或函数与同或函数在逻辑上互为反函数。

- 下述宏模块哪个不包括在MAXpluseI

- 最大等效类是指含状态数目最多的等效类。

- 时序逻辑电路和组合逻辑电路最显著的区别是

- 逻辑代数与普通代数有何异同?

- ECL电路的特点是:()、(),不适合用

- PROCESS语句的启动是由下述哪一类控