试题详情

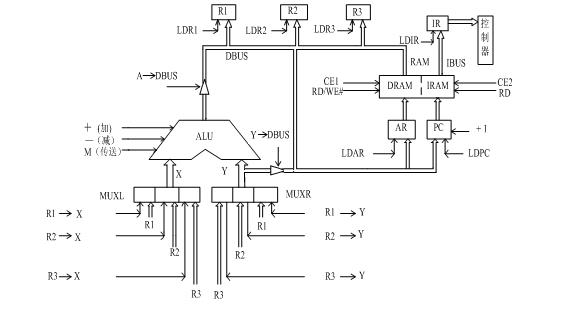

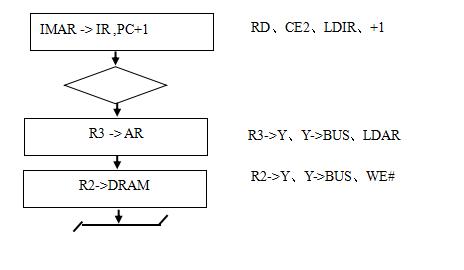

- 简答题一台模拟机的数据通路如图所示,其中ALU完成加、减、传送(X)三种操作,MUX是三选一多路开关,R1~R3是通用寄存器。RAM是双端口存储器,其中DRAM为数据存储器(CE1为读写使能,RD/WE#为读/写命令),IRAM为指令存储器(只读)。AR为数据地址存储器,PC为程序计数器(具有自动加1功能),IR为指令寄存器。所有的单箭头为控制微命令。画出存数指令“STA(R3),R2”的指令周期流程图,标明建立数据通路的微命令。PC中已存放指令地址,DRAM的数据地址由R3提供,写入数据由R2提供。

关注下方微信公众号,在线模考后查看

热门试题

- 已知:X=-0.1011,Y=0.110

- Cache做在CPU芯片内有什么好处?

- 假设同一套指令集用不同的方法设计了PCA

- 高速缓存友好代码基于的原理是()

- 简述CPU维护的相关知识。

- 简述相对寻址和立即寻址的特点。

- 总线的分类有哪些?

- 主机与I/O设备传送数据时,采用(),主

- 用机器语言编写的程序不可以由计算机直接执

- 机器主频周期是指()。

- 计算机中完整的浮点加减运算包括()个步骤

- ()负责协调并控制计算机各部件执行程序的

- -3的补码是()

- 以下不属于非易失性存储器的是()

- CPU与中速的外围设备之间的数据交换通常

- 指令地址码可分为几部分,常用的有()。

- CPU从主存取出一条指令并执行该指令的时

- 一个总线传输周期包括()

- 所有的操作系统具有四个基本特征()。

- 什么情况下需要总线仲裁?总线仲裁的目的是