试题详情

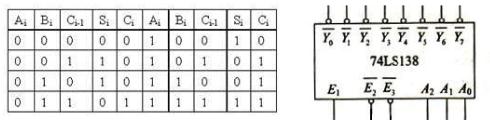

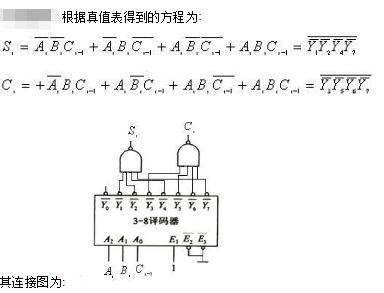

- 简答题已知全加器真值表和74LS138译码器如下图所示,试用一片74LS138译码器和尽可能少的门电路实现其全加器的功能。其中Ai、Bi为加数,Ci-1为低位来的进位,Si为本位和,Ci为向高位的进位。(要求:写出简要的分析过程,并画出电路图)

关注下方微信公众号,在线模考后查看

热门试题

- 仅具有“保持”和“翻转”功能的触发器是(

- 欲使JK触发器按Qn+1

- 按照相邻法编码原则对下表进行状态编码。

- 组合逻辑电路如下图所示: 1

- 逻辑函数F=A⊕(A⊕B)()

- 或门多余端应接地。

- 逻辑代数又称为()代数。最基本的逻辑关系

- 试比较图所示两个逻辑电路的功能。

- 试写出一位全加器的VHDL程序,其结构体

- PLD称为(),它是有与阵列和()组成的

- 函数的反函数=()

- 采用5V电源的TTL器件的高电平范围为(

- Mealy型时序逻辑电路的输出是()的函

- 下列各函数等式中无冒险现象的函数式有()

- 二进制译码器和二-十进制译码器,对应于一

- 与门多余端应接电源。

- 消除组合逻辑电路中险象的常用方法有增加惯

- 已知函数的逻辑表达式怎样得到它的卡诺图?

- 欲使JK触发器按Qn+1

- 组合逻辑电路输出与输入的关系可用()描述