试题详情

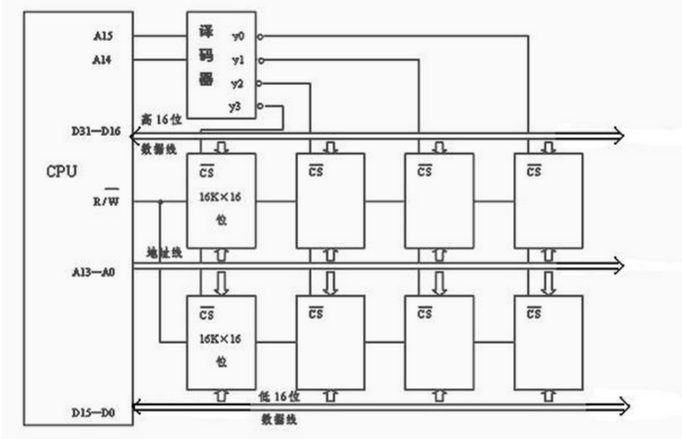

- 简答题用16K×16位的SRAM芯片构成64K×32位的存储器。要求画出该存储器的组成逻辑框图。

-

所需芯片总数(64K×32)÷(16K×16)=8片因此存储器可分为4个模块,每个模块16K×32位,各模块通过A15、A14进行2:4译码

所需芯片总数(64K×32)÷(16K×16)=8片因此存储器可分为4个模块,每个模块16K×32位,各模块通过A15、A14进行2:4译码

关注下方微信公众号,在线模考后查看

热门试题

- 假定某计算机工程师想设计一个新CPU,一

- 基本DLX流水线中四个多路选择器的控制端

- 已知x=10,y=–6

- 多数I/O系统的结构应面向操作系统设计,

- Cache失效中必定包含容量失效。

- 什么是闪速存储器?它有哪些特点?

- 始终只让第K+1条指令的“分析”与第K条

- 多处理机在结构与并行性方面与阵列处理机有

- 试以系列机为例,说明计算机系统结构、计算

- 假设某程序中Load指令占26%,Sto

- 前有一种日渐普及的测试程序产生方法,就是

- 简述全相联映象规则。

- 数据通路出错引起的中断是()

- 为了便于实现多级中断,保存现场信息最有效

- 利用时间重叠概念实现并行处理的是()

- 设x=-0.01011,y=0.0101

- 采用多处理机的一致性机制实现旋转锁有什么

- 按照同一时间内各段之间的连接方式来对流水

- 由汇编语言写成的程序叫做汇编程序。

- 数据通路宽度指的是二次分配总线期间所传送