试题详情

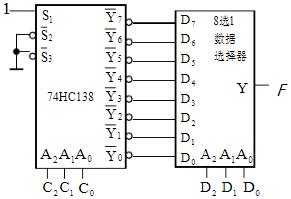

- 简答题图所示是由3线8线译码器74HC138和8选1数据选择器构成的电路。试分析 ①当数据C2C1C0=D2D1D0时,输出F ②当数据C2C1C0≠D2D1D0时,输出F

- ①当数据C2C1C0=D2D1D0时,输出F=0

②当数据C2C1C0≠D2D1D0时,输出F=1 关注下方微信公众号,在线模考后查看

热门试题

- 试将2048×2位的RAM扩展为2048

- 通常将最大干扰信号的幅度称为()

- Moore和Mealy型时序电路的本质区

- 将公共数据线上的数据根据需要送到不同的通

- 将一个时间上连续变化的模拟量转换为时间上

- 最小项,顾名思义就是指的乘积项中变量个数

- 按照数据写入方式特点的不同,ROM可分为

- 对逻辑函数利用代入规则,令A=BC代入,

- 请说出SRAM和DRAM在本质上的不同。

- 下列器件中,属于时序部件的是()

- 试分析下图所示传输门构成的电路,写出其逻

- 由传输门组成的电路如下图所示,试列出其真

- 将下列二进制数转换成十进制数、八进制数和

- VHDL中存在两种延时类型:()延时和(

- 用D触发器构成按循环码(000→001→

- 简述大规模数字逻辑电路设计中的自下而上设

- 计数模为2n的扭环计数器所需的触发器为n

- 在数字信号的接收中,有时需要接收一组特定

- 分析下列逻辑电路功能,写出真值表、表达式

- 请设计一个序列信号发生器,该电路能在时钟