试题详情

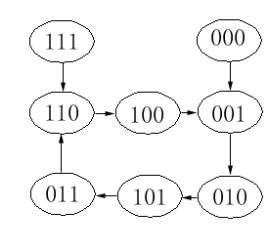

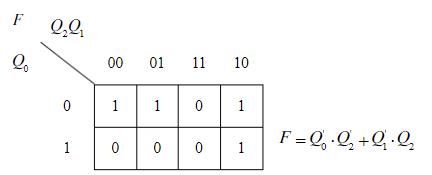

- 简答题请设计一个序列信号发生器,该电路能在时钟信号CP作用下,周期性输出“110010”的串行序列信号;要求采用最小风险方法设计;采用D触发器和必要门电路实现并画出电路原理图。

-

关注下方微信公众号,在线模考后查看

热门试题

- CMOSOD门(漏极开路门)的输出端可以

- 某RAM的地址线为11位,

- 设输入只有原变量没有反变量,试用或非门实

- 分析下面的电路,完成下面的问题 1.根据

- IspLSI器件中,缩写字母GLB是指(

- 全加器属于时序电路。

- 逻辑函数化简的目的是()

- 简述时序仿真的作用及目的。

- 为什么要进行组合逻辑电路的分析?

- 逻辑函数的对偶函数是()

- 利用反馈归零法获得N进制计数器时,若为异

- FLEX10K器件中的FastTrack

- ROM电路由地址译码器和存储体构成,若译

- 只可进行一次编程的可编程器件有()

- 简述时序逻辑电路与组合逻辑电路的主要区别

- 就编程原理而言,FPGA与PAL和GAL

- 断电后()中的信息会丢失。

- 列电路中,实现逻辑功能的是()

- n级触发器构成的环形计数器,其有效循环的

- 逻辑函数F=A⊕(A⊕B)()