试题详情

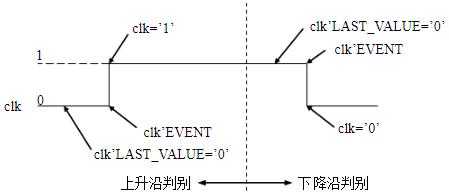

- 简答题根据下图,对上升沿判别和下降沿判别进行分析,并编写进行相关判别的语句。

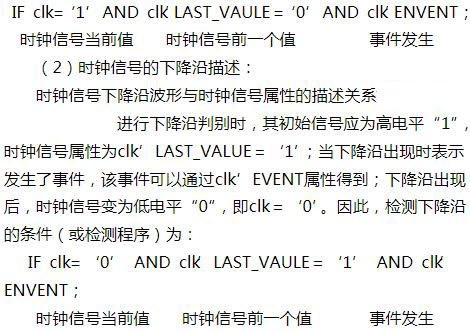

- (1)时钟信号的上升沿描述:进行上升沿判别时,其初始信号应为低电平“0”,时钟信号属性为clk’LAST_VALUE=‘0’;当上升沿出现时表示发生了事件,该事件可以通过clk’EVENT属性得到;上升沿出现后,时钟信号变为高电平“1”,即clk=‘1’。因此,检测上升沿的条件(或检测程序)为:

关注下方微信公众号,在线模考后查看

热门试题

- 下图所示为两种十进制数代码转换器,输入为

- 组合逻辑电路消除竞争冒险的方法有()

- 下列四种类型的逻辑门中,可以用()实现三

- 通常将最大干扰信号的幅度称为()

- 下述哪些器件不属于复杂PLD()

- 为了把时序电路的逻辑功能直观、形象地显示

- (35.4)8=(

- 根据需要将多路数据中的某一种送到公共数据

- 在时间和幅度上都断续变化的信号是数字信号

- 用代数法将逻辑函数F化简为最简&ldqu

- 设计1110序列检测器的状态转换图,并求

- 按照数据写入方式特点的不同,ROM可分为

- 用卡诺图化简下列逻辑函数

- 若RAM的地址码有8位,行、列地址译码器

- 在信号属性函数中,s’LAST_ACTI

- 试说明CMOS逻辑电路输入端不能悬空?

- 若干个具有三态输出的电路输出端接到一点工

- 常见的化简方法有()三种。

- JTAG是指联合()行动组。

- 构造一个模10同步计数器,需要()触发器