试题详情

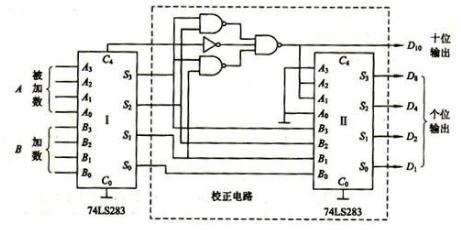

- 简答题试用二进制四位全加器74LS283实现一位8421BCD码的加法器电路。

关注下方微信公众号,在线模考后查看

热门试题

- 对编译器来说,每个设计项目必须有一个单独

- 随机存取存储器具有()功能。

- 在数字电路中为什么要采用二进制?它有何特

- 试比较C语言和VHDL语言的区别。

- 采用JK触发器组成电路,得到如图所示的输

- 四选一数据选择器74LS153可以作为函

- 一位8421BCD码计数器至少需要()个

- 欲使JK触发器按Qn+1=0工作,可使J

- ()的8421码为01001001011

- 有一个移位寄存器,高位在左,低位在右,欲

- 已知函数的对偶式为 ,则它的原函数是什

- 组合电路与时序电路的主要区别()

- 在下列逻辑部件中,不属于组合逻辑部件的是

- 为了把时序电路的逻辑功能直观、形象地显示

- 简述CPLD/FPGA的原理、特点与应用

- 或门多余端应接地。

- 或非门构成的基本RS触发器,输入端SR的

- 有一个容量为256×4位的RAM,该RA

- 当用异步I/O输出结构的PAL设计逻辑电

- 对于钟控RS触发器,若要求其输出“0”状