试题详情

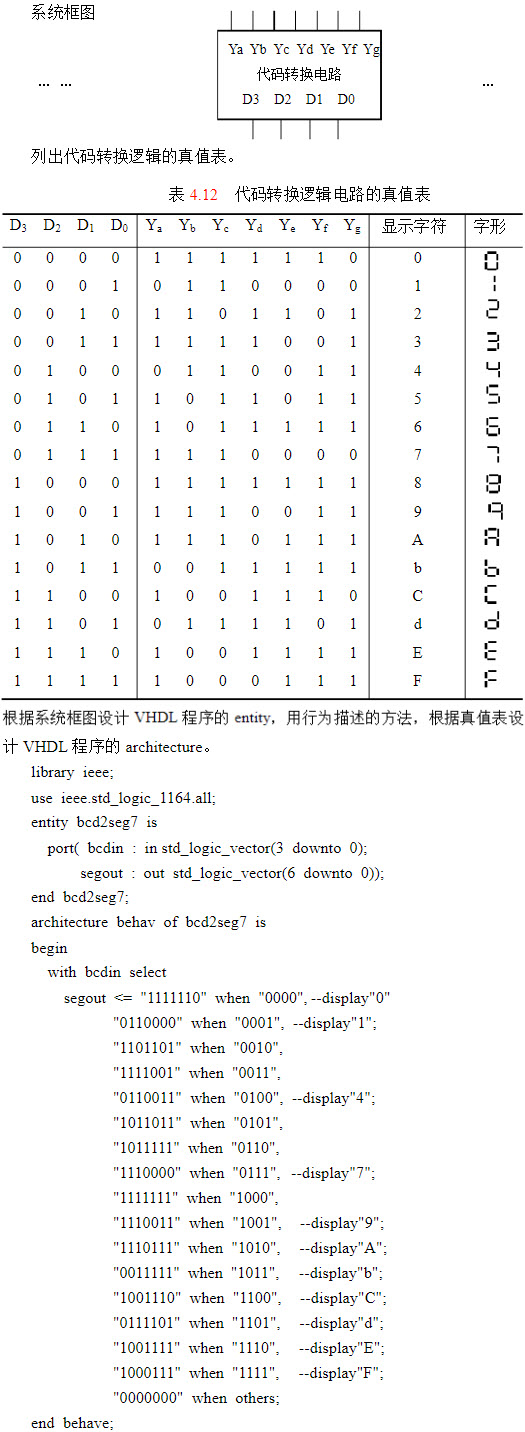

- 简答题用VHDL设计一个代码转换逻辑电路。把4位二进制代码转换成7段字符显示代码。能显示数字0~9和字母A,b,C,d,E,F。

- 电路的输入是4位代码,输出是7位代码。用D3~D0作为输入信号名,用Ya~Yg作为输出信号名,分别对应a、b、c、d、e、f、g这7个段。

关注下方微信公众号,在线模考后查看

热门试题

- 若用4位字长来表示,(-5)D=()原=

- 测得某逻辑门输入A、B和输出F的波形如下

- 采用串行加法器比采用并行加法器的运算速度

- 下表是一个2选1电路真值表,请根据表中给

- 设计一个“四舍五入”电路。该电路输入为1

- 对于T触发器,若原态Qn=0,欲使新态Q

- =()

- 三态门有三种输出状态(即输出高电平、输出

- 寄存器按照功能不同可分为两类:()寄存器

- 常用的BCD码有()、()、()、()等

- 试述VHDL程序中实体和结构体的相互关系

- 某产品有A、B、C、D四项质量指标。规定

- 若函数F和函数G的卡诺图相同,则函数相等

- 分析如图所示同步时序逻辑电路,说明该电路

- 用代数法求出下列逻辑函数的最简&ldqu

- 某热水器如下图所示:图中虚线表示水位,A

- 用卡诺图判别逻辑函数Y和Z之间的关系:

- 分析下图所示的逻辑电路图,说明该电路的逻

- 我们一般将竞争分为()两种。

- 设计一个按自然态序变化的7进制同步加法计