试题详情

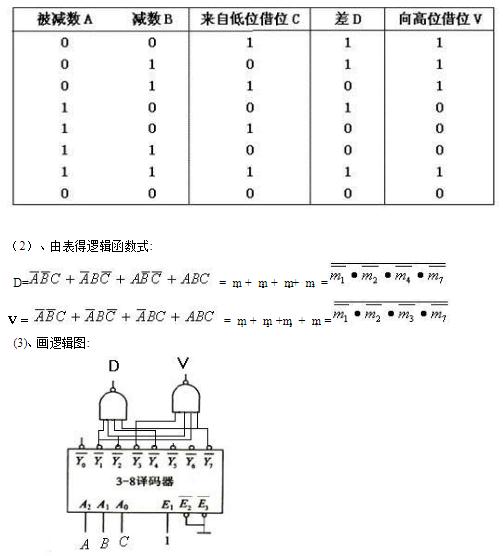

- 简答题用3线——8线译码器74LS138和门电路设计1位二进制全减器电路。输入为被减数、减数和来自低位的借位;输出为两数之差和向高位的借位信号。

- (1)列真值表:

关注下方微信公众号,在线模考后查看

热门试题

- 最大等效类是指含状态数目最多的等效类。

- 卡诺图在构造上有何特点?

- 已知某同步时序电路的激励函数和输出函数表

- 某机床共有4个电气开关(断为0,通为1)

- 同步时序电路没有统一的时钟脉冲控制。

- 组合逻辑电路设计:设ABC为某保密锁的三

- (48)10=()

- 试用3线-8线译码器74HC138和门电

- 等效状态和相容状态均具有传递性。

- 向8位集成DAC0832输入二进制数据“

- 在VHDL的运算操作符中,NOT的优先级

- 在数字电路中,常用的计数制除十进制外,还

- 元件例化的作用是什么?

- 下述那一种不是MAXpluseII编译器

- 由与非门组成的基本RS触发器,不允许输入

- 函数其反函数()对偶式()

- 触发器的逻辑功能可用()、()、()和时

- 译码器的逻辑功能是将某一时刻的()输入信

- 用VHDL设计一个模为12的加法计数器,

- 二进制数1101.1011转换为八进制为