试题详情

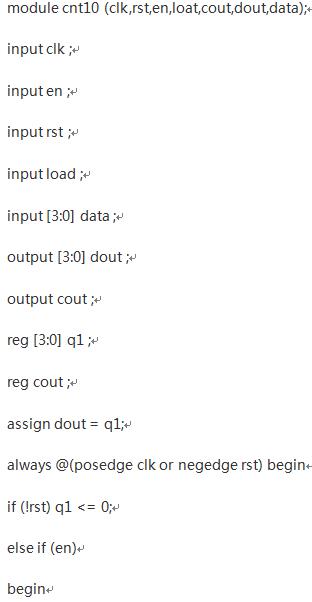

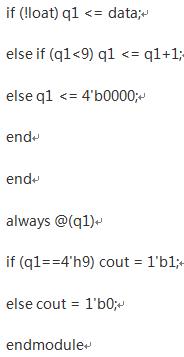

- 简答题设计一个带有异步复位控制端和时钟使能控制端的10进制计数器。端口设定如下:输入端口:CLK:时钟,RST:复位端,EN:时钟使能端,LOAD://置位控制端,DIN:置位数据端;输出端口:COUT:进位输出端,DOUT:计数输出端。

-

关注下方微信公众号,在线模考后查看

热门试题

- 元件实例语句“notif1#(1:3:4

- 简述基于数字系统设计流程包括哪些步骤?

- P,Q,R都是4bit的输入矢量,下面哪

- 下列标识符中,()是不合法的标识符。

- 在case语句中至少要有一条()语句

- 根据下面的程序,画出产生的信号波形。

- 关于函数的描述下列说法不正确的是()

- EDA缩写的含义为()

- 系统函数和任务函数的首字符标志为(),预

- 用assign描述的语句我们一般称之为(

- CPLD

- 设计一个带有异步复位控制端和时钟使能控制

- Verilog HDL语言进行电路设计方

- 编程实现带同步清0、同步置1的D触发器。

- 完整的条件语句将产生()电路,不完整的条

- 可编程逻辑器件的优化过程主要是对()和资

- 在进程中什么情况下综合为时序电路?什么情

- 下列语句中,不属于并行语句的是:()

- 你所知道的可编程逻辑器件有(至少两种):

- 编程实现两个4位二进制数相减的程序。